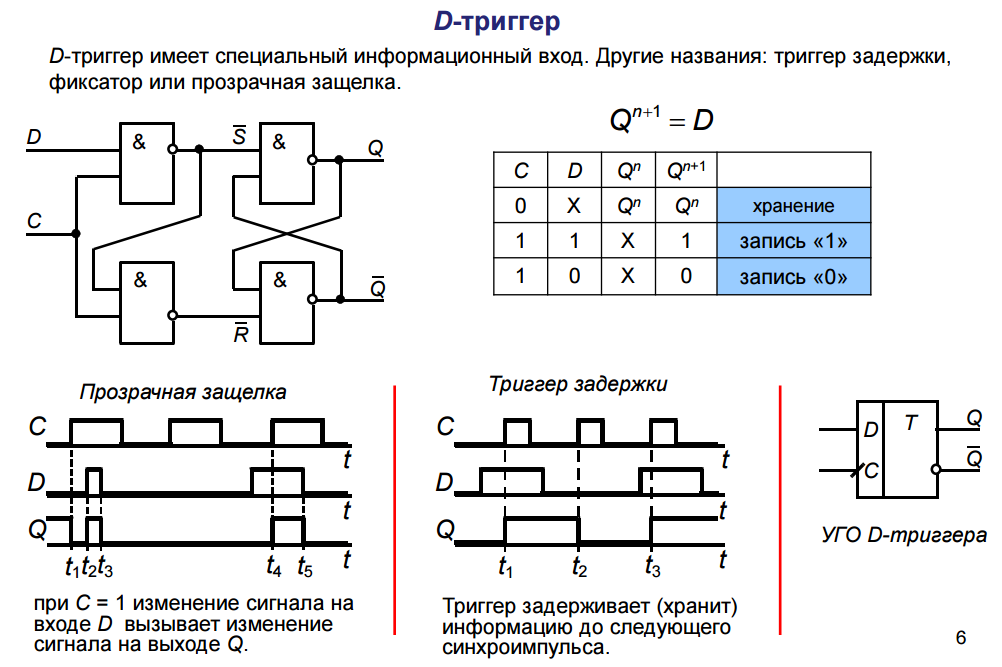

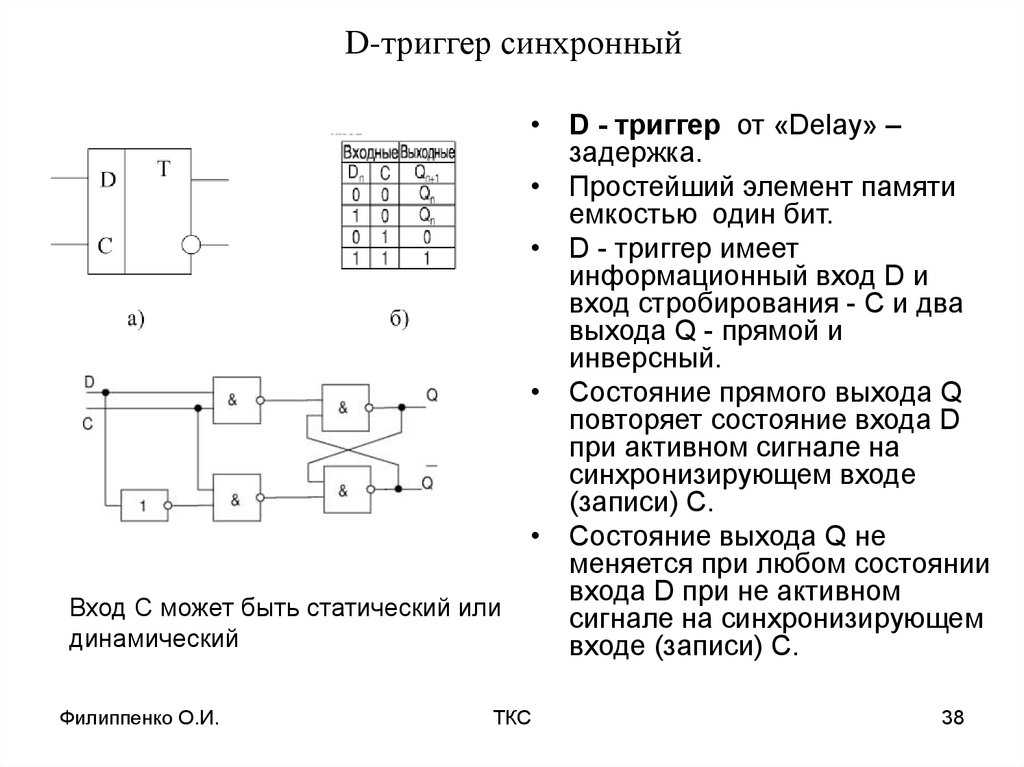

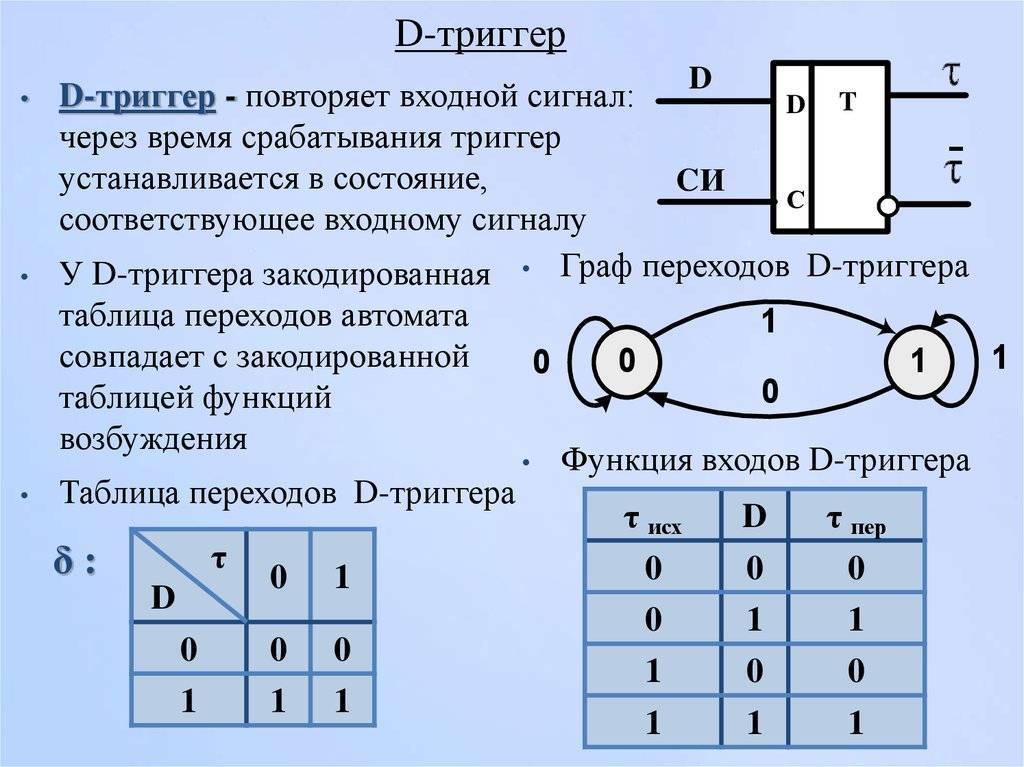

D-триггер

D-триггер (от англ. delay) запоминает входную информацию при поступлении синхроимпульса.

Хранение информации в D-триггерах обеспечивается за счет синхронизации, поэтому все реальные D-триггеры имеют два входа: информационный D и синхронизации С (рис. 12). Под действием синхросигнала С информация, поступающая на вход D, принимается в триггер, но на выходе Q появляется с задержкой на один такт. В D-триггере с динамическим входом прием в триггер информации со входа D происходит в момент смены на входе С уровня 0 на уровень 1.

Рис. 12 – Схема D-триггера

Таблица 3

| C | D | Qt+1 |

|---|---|---|

| 1 | ||

| 1 | 1 | 1 |

Условное графическое обозначение D-триггера показано на рис. 13.

Рис. 13 – Условное графическое обозначение D-триггера

Так как информация на выходе остается неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защелкой. Легче всего объяснить появление этого названия по временной диаграмме, приведенной на рисунке 14.

Рис. 14 – Временная диаграмма D-триггера

По этой временной диаграмме видно, что триггер-защелка хранит данные на выходе только при нулевом уровне на входе синхронизации. Если же на вход синхронизации подать активный высокий уровень, то напряжение на выходе триггера будет повторять напряжение, подаваемое на вход этого триггера. Входное напряжение запоминается только в момент изменения уровня напряжения на входе синхронизации C с высокого уровня на низкий уровень. Входные данные как бы “защелкиваются” в этот момент. Отсюда и название – триггер-защелка.

Принципиально в этой схеме входной переходной процесс может беспрепятственно проходить на выход триггера

Поэтому там, где это важно, необходимо сокращать длительность импульса синхронизации до минимума. Чтобы преодолеть такое ограничение были разработаны триггеры, работающие по фронту

Схема такого триггера приведена на рисунке 15, а обозначение на принципиальных схемах на рисунке 16.

Рис. 15 – Схема универсального D-триггера

Рис. 16 – Обозначение универсального D-триггера на принципиальных

схемах

На рис. 17 представлено условное обозначение D-триггера микросхемы К155ТМ2, содержащей два D-триггера. Входы R и S выполняют те же функции, что и в RS-триггере.

Рис. 17 – D-триггер микросхемы К155ТМ2

D-триггер несложно преобразовать в счетный триггер, т. е. такой, состояние которого изменяется после поступления очередного импульса на счетный вход. Для обеспечения счетного режима необходимо вход D соединить с инверсным выходом триггера (рис. 18,а). Из логики работы

D-триггера следует, что после прихода импульса на вход С состояние

триггера будет изменяться на противоположное. Это иллюстрируется

временными диаграммами, или эпюрами напряжений (рис. 18,б). Подобно

таблице истинности, эпюры напряжений дают наглядное представление о работе

устройства.

Рис. 18 – Работа D-триггера в счетном режимеа) – соединение выводов, б) – временные диаграммы

Необходимо отметить, что изменение состояния D-триггера данного типа происходит при изменении напряжения на счетном входе с низкого уровня на высокий. Такое изменение

напряжения часто называют положительным перепадом напряжения или фронтом импульса. Реакцию триггера на положительный перепад напряжения отображают

косой чертой, пересекающей линию входа С (рис. 18,а). Аналогично

изменение напряжения с высокого уровня на низкий называют отрицательным

перепадом напряжения, спадом или срезом импульса. На схемах это отображают

также косой чертой, но повернутой на 90° относительно показанной на

рисунке 18,а. В зависимости от своей внутренней структуры триггер реагирует или

на положительный, или на отрицательный перепад напряжения.

Различия в функциональных возможностях

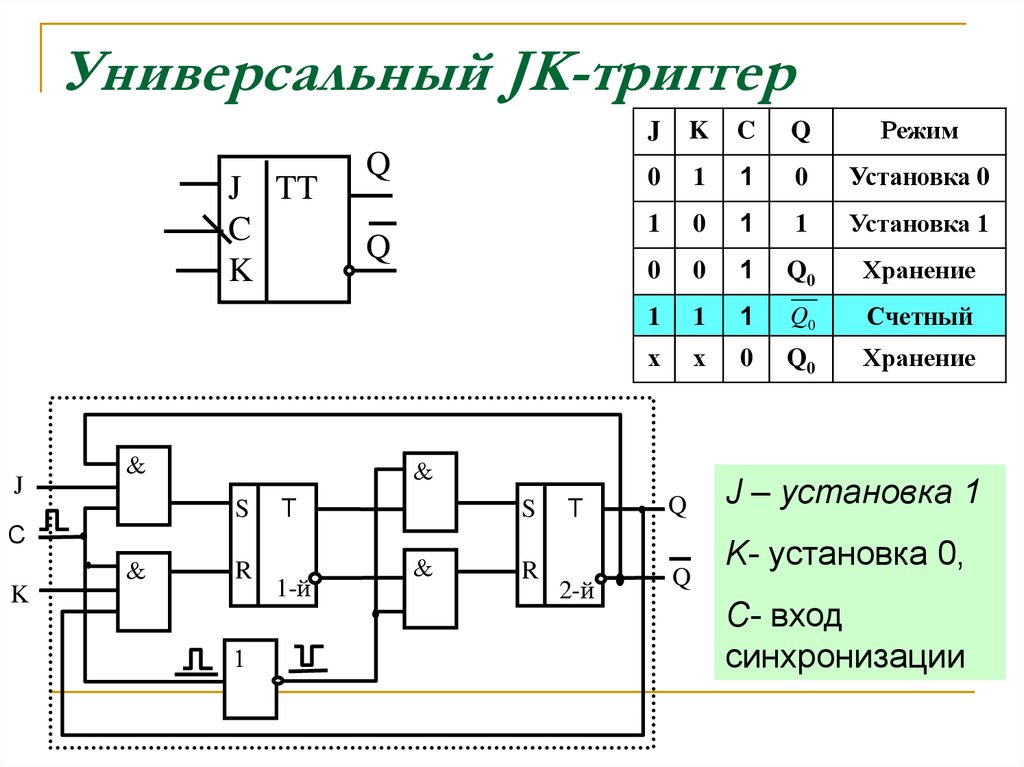

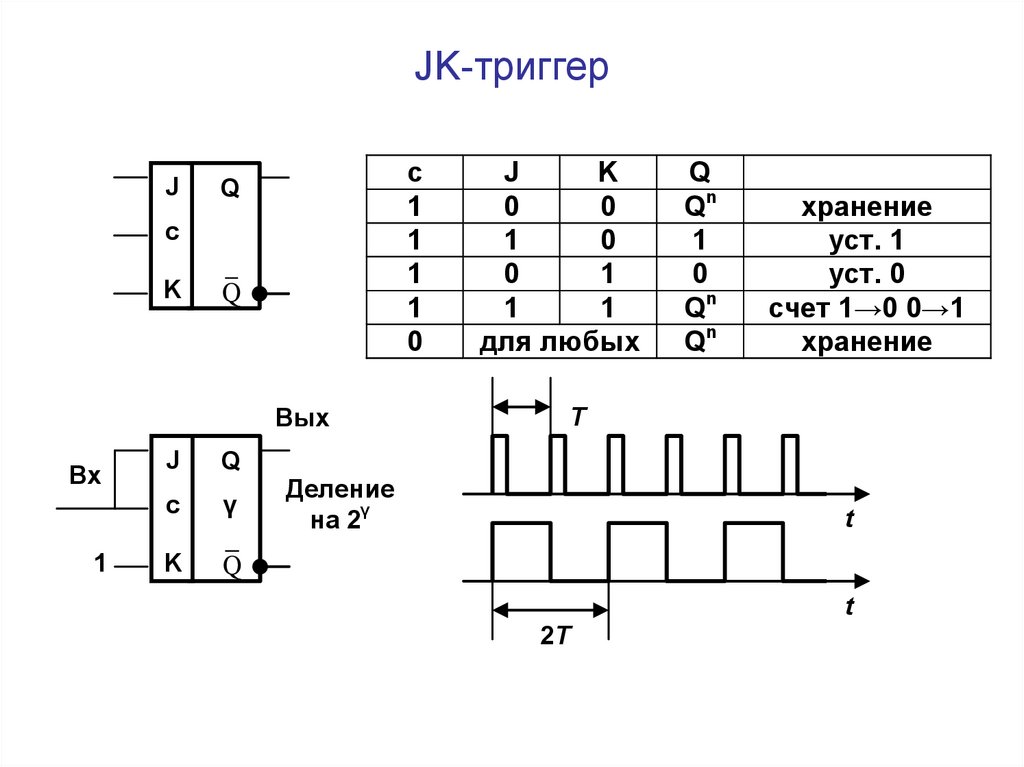

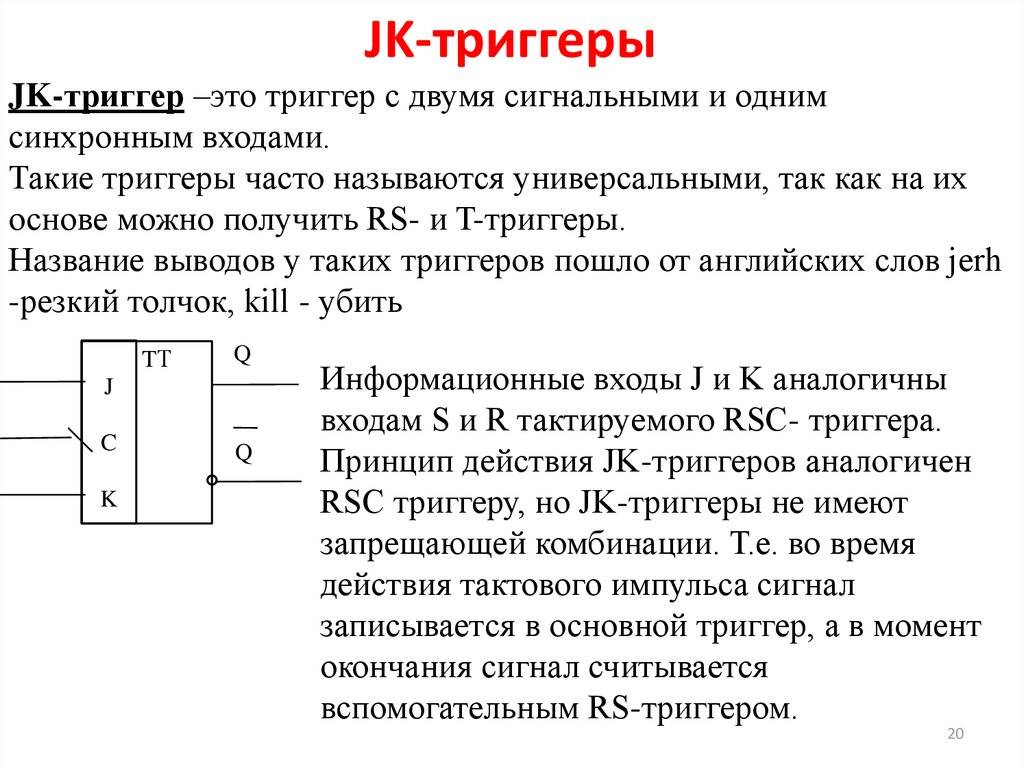

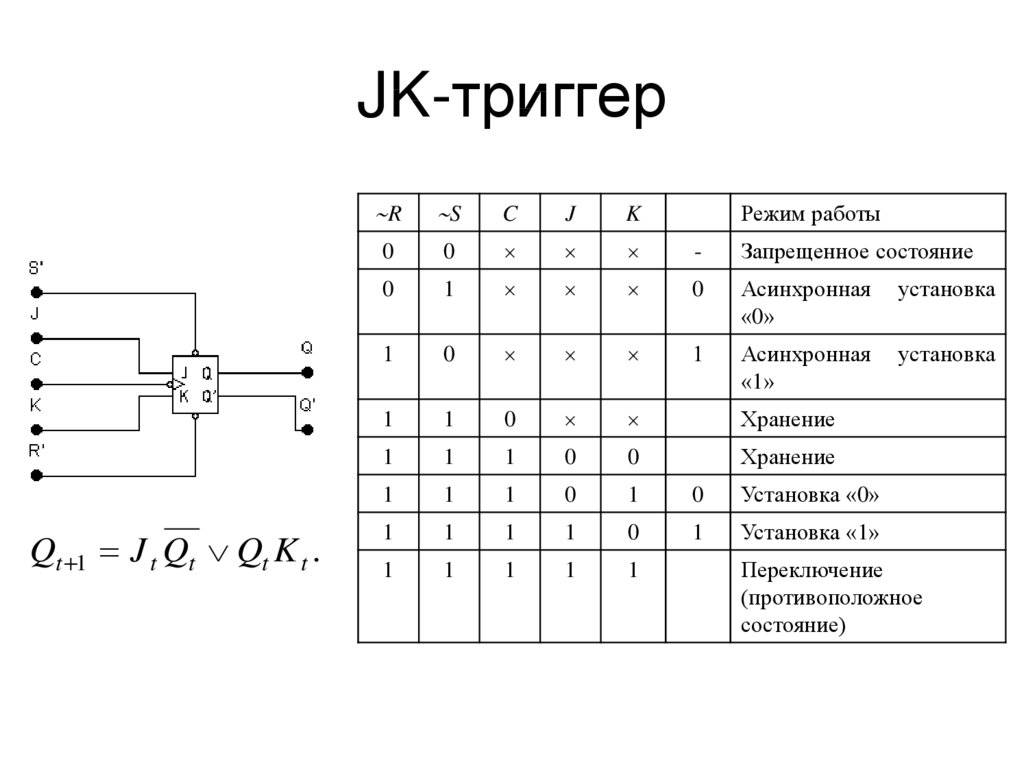

- Состояние хранения: Одним из ключевых различий между JK-триггером и RS-триггером является их способность сохранять состояние. RS-триггер хранит состояния «0» и «1», а также имеет состояние «запрещено» (иногда обозначается как «X»). JK-триггер же может хранить все четыре возможных состояния — «00», «01», «10» и «11». Это делает JK-триггер более гибким в использовании.

- Режим работы: RS-триггер является управляемым триггером. Он имеет два входа: S (set) и R (reset), с помощью которых можно установить или сбросить его состояние. Наоборот, JK-триггер является триггером с автоматической работой, в котором состояние изменяется при каждом положительном фронте тактирующего сигнала. Он имеет три входа: J (set), K (reset) и CLK (тактовый), что позволяет контролировать и изменять его состояние.

- Функциональные возможности: JK-триггер обладает дополнительными функциональными возможностями по сравнению с RS-триггером. Например, он может быть использован для создания счетчиков, делителей и других последовательностей, благодаря возможности вводить различные комбинации сигналов на его входы J и K. Это делает JK-триггер более универсальным и гибким элементом для различных цифровых схем.

Таким образом, отличия в функциональных возможностях между JK-триггером и RS-триггером заключаются в их способности хранить состояние, режиме работы и дополнительных функциях, которые предлагает JK-триггер.

Отличия jk триггера от rs триггера

Одно из основных отличий между JK-триггером и RS-триггером заключается в их способности предотвратить состояние метастабильности — неустановленное состояние выходных сигналов в результате неправильных входных комбинаций. RS-триггер может попасть в метастабильное состояние, если на его входы подаются недопустимые комбинации сигналов, тогда как JK-триггер способен предотвратить метастабильность за счет использования дополнительной обратной связи.

Еще одно отличие между этими триггерами заключается в функциональных возможностях. JK-триггер обладает более широким набором функций, таких как возможность установить значение на входах, установка и сброс значения. Кроме того, JK-триггер может использоваться в режиме счётчика с отключенным входом сброса, что позволяет ему работать в качестве двухтактного триггера. RS-триггер, с другой стороны, имеет только два состояния: установленное и сброшенное.

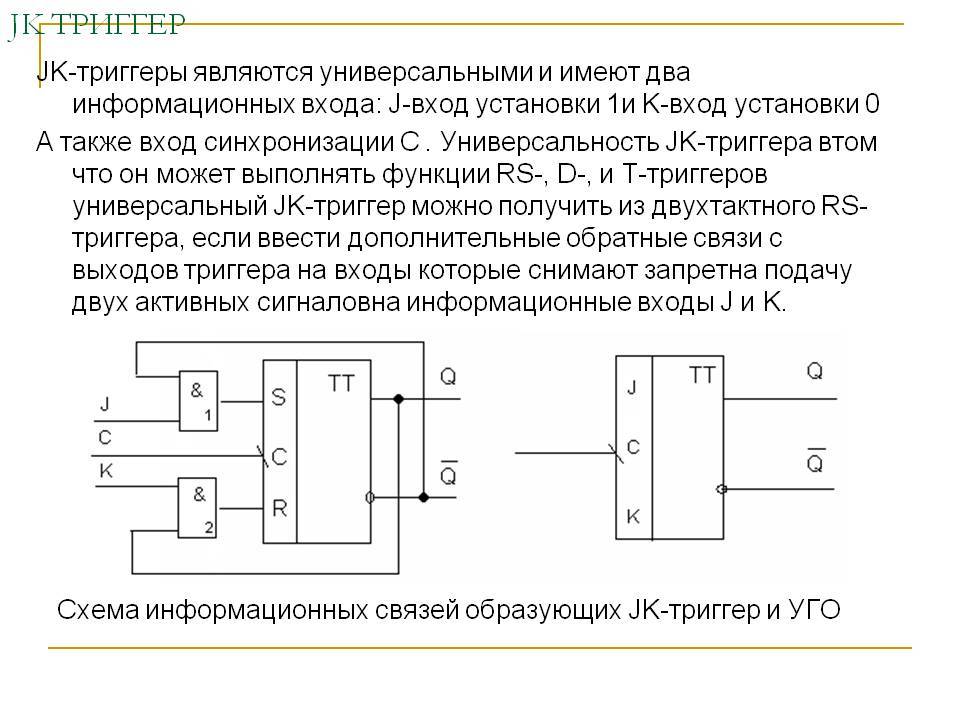

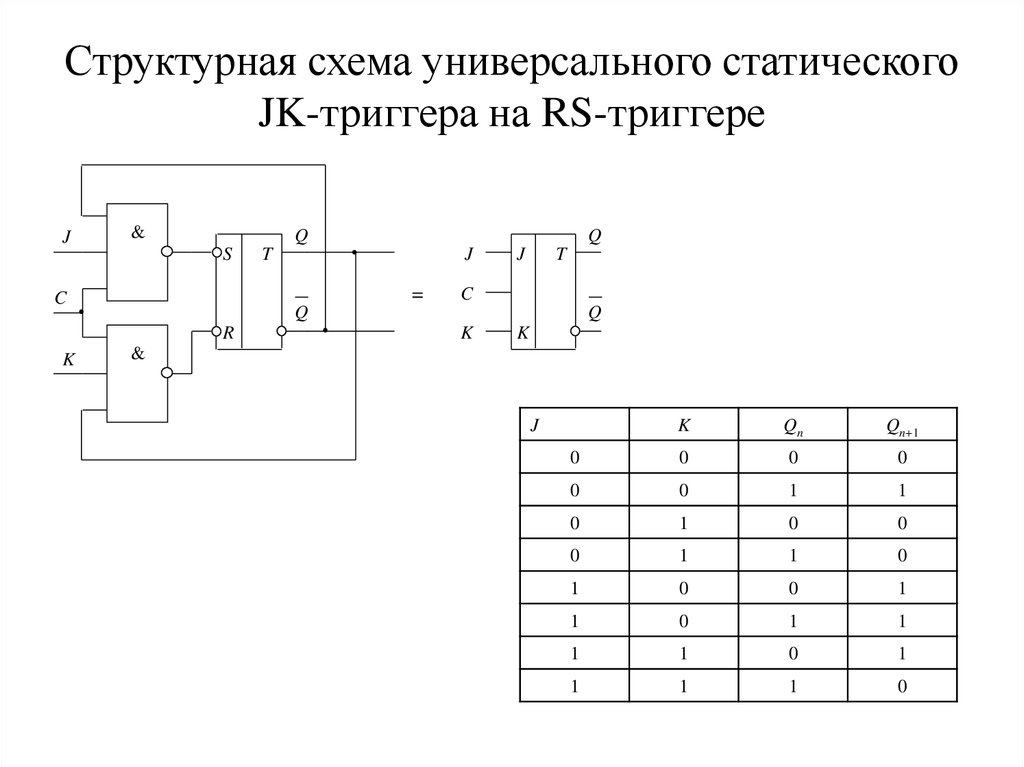

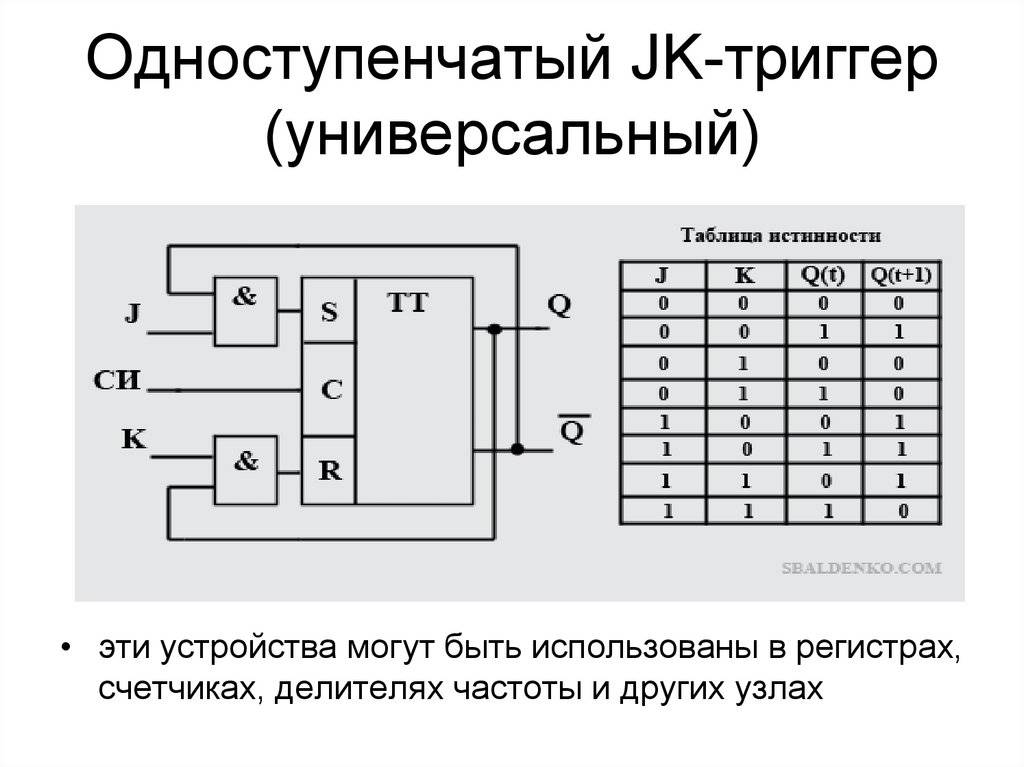

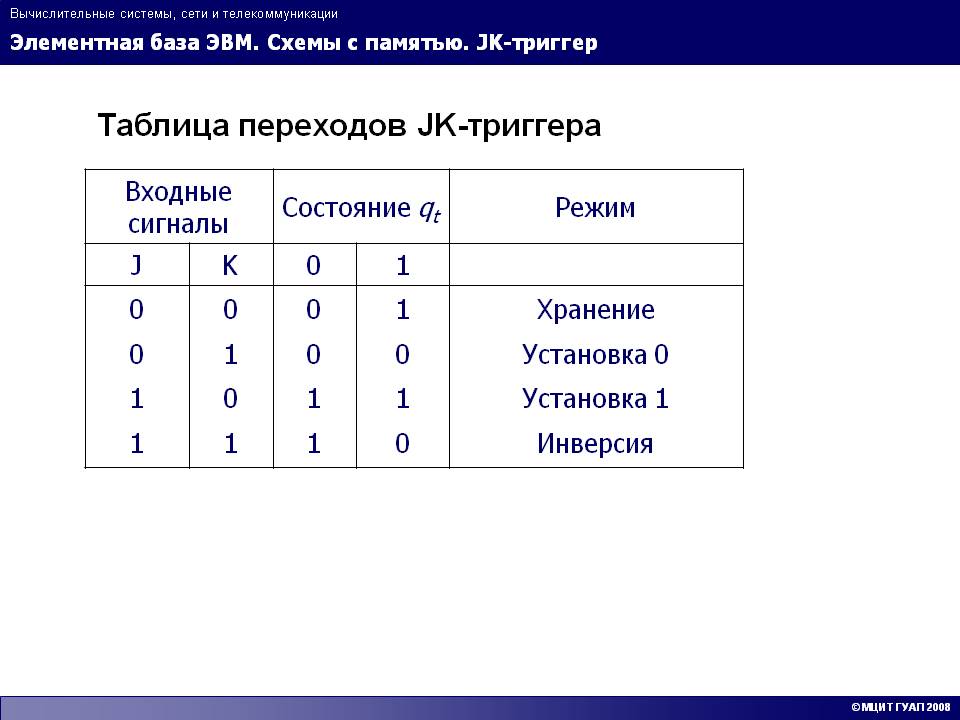

Принцип работы JK-триггера

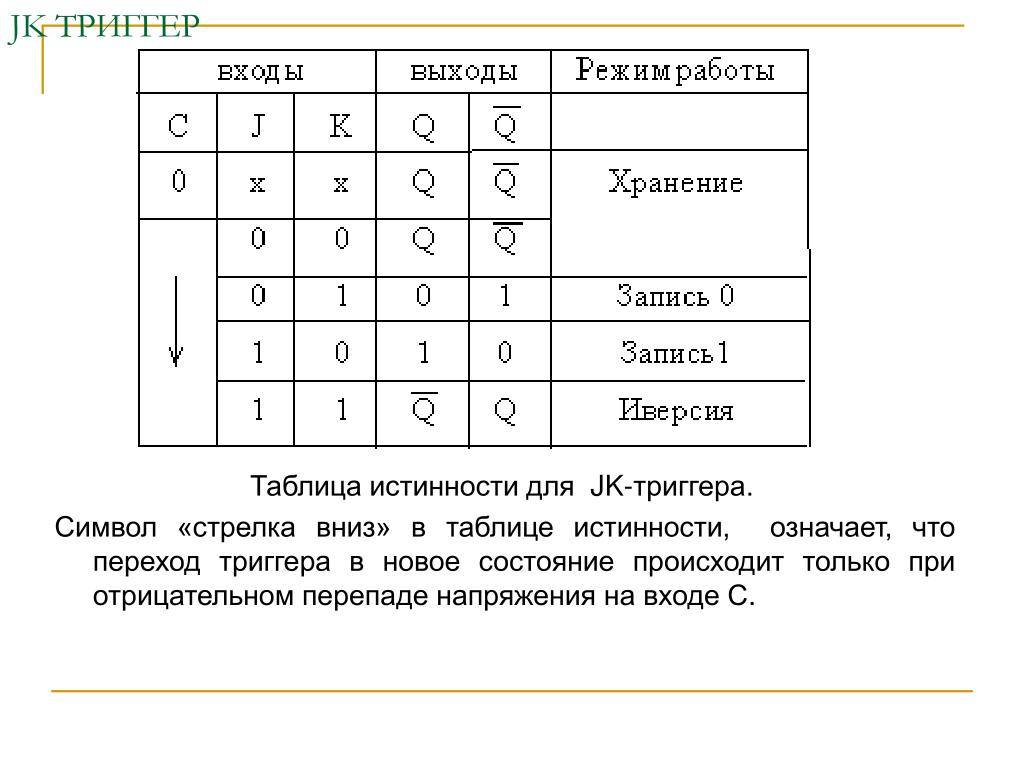

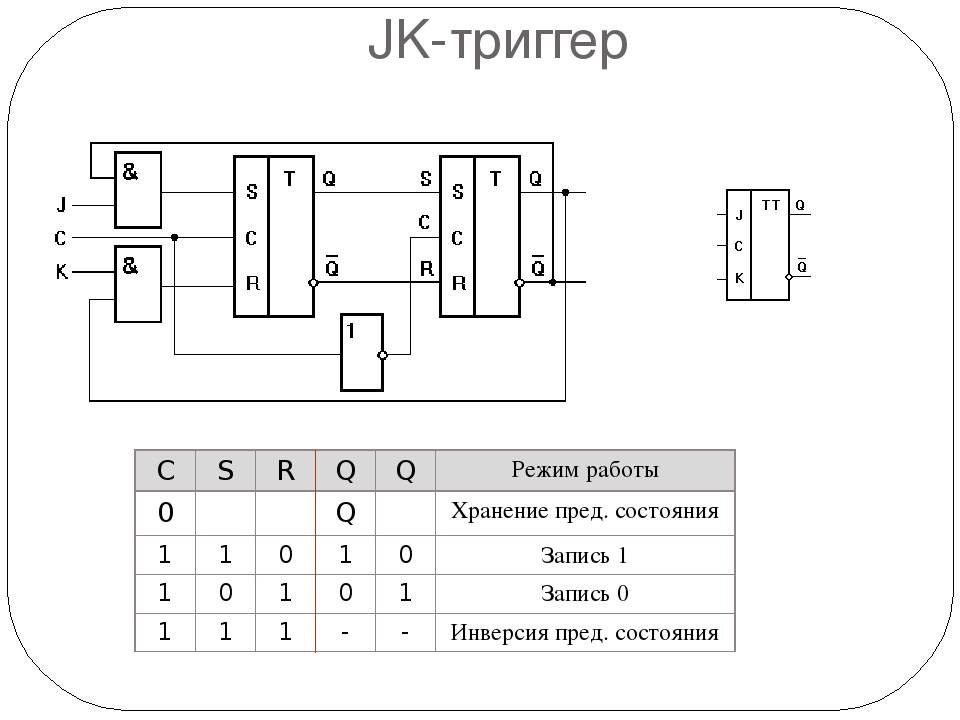

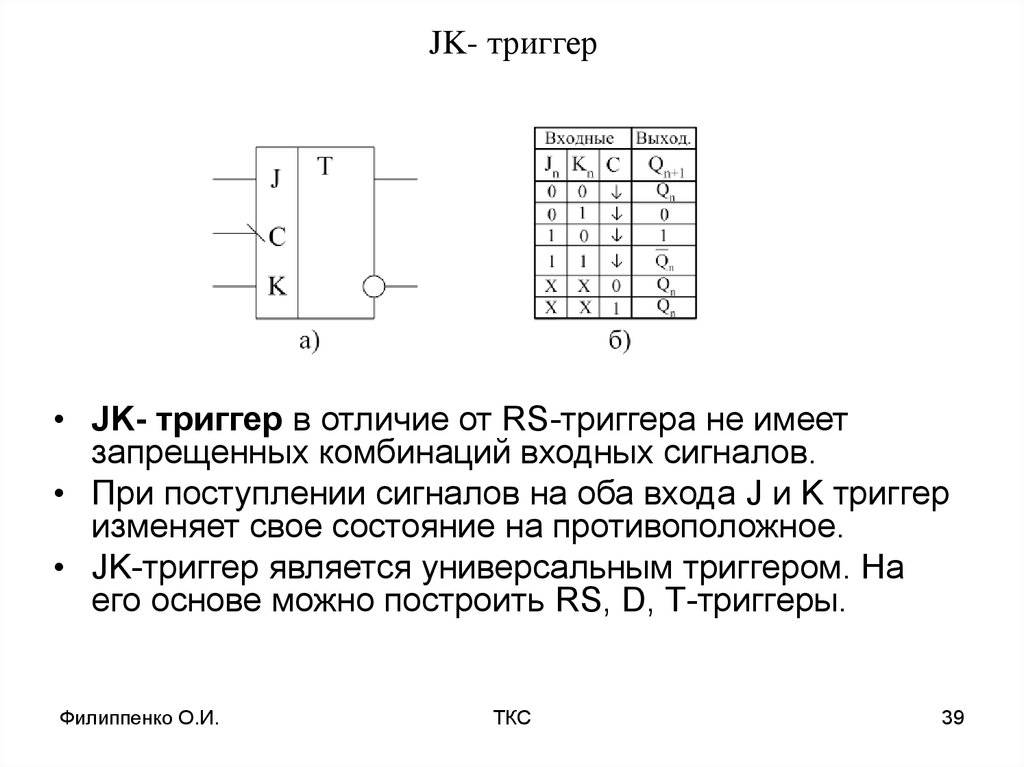

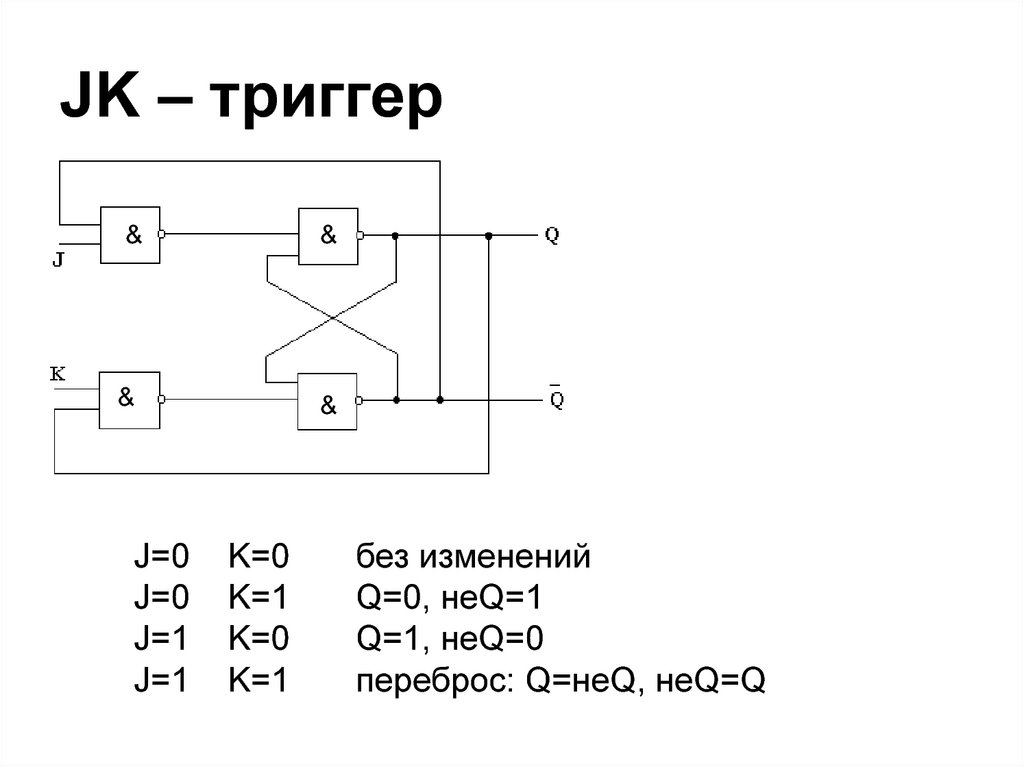

JK-триггер представляет собой цифровую электронную схему, которая используется в цифровых устройствах для хранения, обработки и передачи информации. Он состоит из двух входов J и K, выхода Q и инверсного выхода Q̅.

Основная идея работы JK-триггера заключается в том, что он может быть использован для создания режима отслеживания (логического уровня на выходе сохраняется до появления нового входного сигнала) или режима переключения (логический уровень на выходе меняется при появлении определенного комбинации входных сигналов).

Режим отслеживания достигается, когда на входы J и K подается логический нуль (0). В этом случае состояние JK-триггера не меняется, и выходное значение Q сохраняется.

Режим переключения достигается путем установления определенной комбинации на входах J и K. Если на вход J подается логическая единица (1), а на вход K — 0, выходной сигнал Q меняется на противоположный (инвертируется). Если на вход J подается 0, а на вход K — 1, выходной сигнал Q̅ меняется на противоположный.

В случае, когда на входах J и K подается логическая единица (1), происходит переключение состояний JK-триггера, обеспечивая режим тогглинга (инвертированного вывода на каждом такте синхронизации).

Принцип работы JK-триггера основывается на использовании триггерного элемента, такого как транзисторный ключ, для управления выводом Q и Q̅. При изменении состояния на входах J и K, изменяется состояние триггера и записывается новое значение на выходе. Это позволяет использовать JK-триггер для создания последовательных схем, счетчиков и других устройств с памятью и логическими операциями.

Принцип работы и гибкость JK-триггера делают его полезным в различных цифровых приложениях, включая компьютеры, микроконтроллеры, счетчики, сдвиговые регистры и другие устройства, где необходимо хранение и обработка данных.

Транзисторные схемы

Транзисторные схемы работают достаточно похожим образом, и строятся на основе полевых транзисторов с изолированным затвором, так же известные как МОП-транзисторы (MOSFET), выполняющих роль переключателя. Однако, критерием “истинности” или “ложности” всей схемы является не протекающий ток, а значение напряжения (условно “высокое” или “низкое”)

Принципы работы полевых транзисторов

Полевые транзисторы состоят из двух полупроводниковых терминалов p- или n-типа (называемых исток (Source) и сток (Drain)), помещенных в субстрат соответственно n- или p-типа. N-тип соответствует электронной, а p-тип – дырочной проводимости. Сам транзистор обозначается по типу терминалов.

Так же присутствуют два терминала, называемых база (base) и затвор (gate), которые, собственно, и обеспечивают управление транзистором.

При приложении напряжения между базой и затвором, электроны или дырки притягиваются к области затвора, создавая канал проводимости между истоком и стоком. Изменение электрического поля между базой и затвором изменяет сопротивление этого канала.

Встречаются МОП-транзисторы с собственным (или встроенным) (depletion mode transistor) и индуцированным (или инверсным) каналом (enhancement mode transistor). Встроенный канал означает, что при нулевом напряжении затвор-база, канал транзистора открыт (т.е. проводит ток); для закрытия канала нужно приложить к затвору напряжение определенной полярности. Канал приборов с индуцированным каналом закрыт (не проводит ток) при нулевом напряжении затвор-база; для открытия канала нужно приложить к затвору напряжение определенной полярности. Полярность напряжения определяется типом проводников в транзисторе (N- или P-тип).

СИЗБNPPЗСИБ

Схема и условное обозначение PMOS с индуцированным каналом

СИЗБPNN

Схема и условное обозначение NMOS с индуцированным каналом

Схема и условное обозначение PMOS с собственным каналом

Схема и условное обозначение NMOS с собственным каналом

Часто терминал базы подключают напрямую к истоку.

Реализация логических операций на МОП-транзисторах

Независимо от типа транзистора, он может быть “настроен” таким образом, чтобы либо переходить в “открытое” состояние при подаче высокого напряжения (соответствующего логической единице) на затвор, либо низкого (соответствующего логическому нулю), и в “закрытое” в противном случае. При проектировании логических схем, имеет значение только этот фактор.

В этом контексте, транзисторы, переходящие в “открытое” состояние при подаче логической единицы на затвор, называются прямыми, а в “закрытое” – инверсными. При проектировании логики, часто используются следующие обозначения:

Прямой МОП-транзистор

Инверсный МОП-транзистор

Как правило, прямые транзисторы реализуются на NMOS, а инверсные – на PMOS.

На основе этих двух типов строятся микросхемы типа CMOS (КМОП – комплементарная структура металл-оксид-полупроводник, она же COS-MOS), состоящие из симметрично расположенных p- и n-канальных полевых транзисторов. Использование симметричных схем позволяет значительно уменьшить ток активации схемы, и снизить энергопотребление.

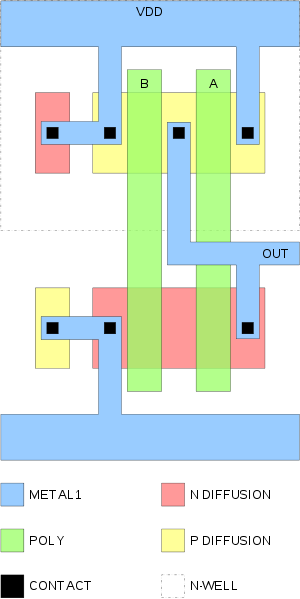

Штрих Шеффера может быть реализован, например, так:

VccF = A | BAB

Штрих Шеффера на прямых транзисторах

VccAVccBF = A | B

CMOS-схема штриха Шеффера

Физическое устройство CMOS-схемы

Физическое устройство CMOS-схемы

Логические схемы

На основе логических элементов строятся логические схемы. На логических схемах не рассматривается внутреннее устройство элементов, поэтому все логические схемы полностью эквивалентны логическим формулам, которые их выражают.

Для обозначения логических элементов, соответствующих базовым логическим операциям используются следующие обозначения:

&

Конъюнктор, соответствует операции конъюнкции.

1

Дизъюнктор, соответствует операции дизъюнкции.

Инвертор, соответствует операции инверсии.

И-НЕ (NAND), соответствует штриху Шеффера.

ИЛИ-НЕ (NOR), соответствует стрелке Пирса.

Внутреннее устройство триггера

Не вдаваясь в глубину схемотехники триггера, скажу сразу, что простейший триггер представляет собой схему из двух логических элементов, взаимодействуя между собой с помощью положительной обратной связи, которая обеспечивает нахождения выходов триггера в одном их двух логических состояний неограниченное время.

Схема триггерной ячейки на логических элементах (RS триггер).

Как говорилось выше, входы триггера R и S реагируют на низкий логический уровень и сигналы на них должны поступать с некоторой разницей во времени. Опишем работу данной схемы. Когда на обоих входах триггера присутствует низкий логический уровень, то это никак не отразится на уровне напряжения на выходах. Когда на вход S поступит сигнал лог. 1, то на выходах Q будет лог. 0, а на –Q – лог. 1. Если теперь на вход R триггера поступит лог. 1, то выходные сигналы не изменятся. И наконец если изменить уровень сигнала на входе S с высокого на низкий уровень, то на выходе триггера Q будет лог. 1, а на –Q – лог. 0. Таким образом, для данной триггерной ячейки можно составить таблицу истинности.

Таблица истинности триггерной ячейки (RS триггер).

Схемы с такой таблицей истинности называются RS триггерами. RS триггеры служат основой для многих динамических устройств: делители частоты, счётчики, регистры. Кроме вышеописанного RS триггера существует ещё несколько типов триггеров, которые отличаются методом управления, входными и выходными сигналами. Все современные триггеры объединены в серии цифровых микросхем:

- RS триггеры – самый простой и редко используемый триггер, имеет обозначение ТР;

- JK триггер – имеет сложное управление, обозначение ТВ;

- D триггер – самый распространённый и имеет сложность среднюю, обозначение ТМ;

Транзисторные схемы

Транзисторные схемы работают достаточно похожим образом, и строятся на основе полевых транзисторов с изолированным затвором, так же известные как МОП-транзисторы (MOSFET), выполняющих роль переключателя. Однако, критерием “истинности” или “ложности” всей схемы является не протекающий ток, а значение напряжения (условно “высокое” или “низкое”)

Принципы работы полевых транзисторов

Полевые транзисторы состоят из двух полупроводниковых терминалов p- или n-типа (называемых исток (Source) и сток (Drain)), помещенных в субстрат соответственно n- или p-типа. N-тип соответствует электронной, а p-тип – дырочной проводимости. Сам транзистор обозначается по типу терминалов.

Так же присутствуют два терминала, называемых база (base) и затвор (gate), которые, собственно, и обеспечивают управление транзистором.

При приложении напряжения между базой и затвором, электроны или дырки притягиваются к области затвора, создавая канал проводимости между истоком и стоком. Изменение электрического поля между базой и затвором изменяет сопротивление этого канала.

Встречаются МОП-транзисторы с собственным (или встроенным) (depletion mode transistor) и индуцированным (или инверсным) каналом (enhancement mode transistor). Встроенный канал означает, что при нулевом напряжении затвор-база, канал транзистора открыт (т.е. проводит ток); для закрытия канала нужно приложить к затвору напряжение определенной полярности. Канал приборов с индуцированным каналом закрыт (не проводит ток) при нулевом напряжении затвор-база; для открытия канала нужно приложить к затвору напряжение определенной полярности. Полярность напряжения определяется типом проводников в транзисторе (N- или P-тип).

СИЗБNPPЗСИБ

Схема и условное обозначение PMOS с индуцированным каналом

СИЗБPNN

Схема и условное обозначение NMOS с индуцированным каналом

Схема и условное обозначение PMOS с собственным каналом

Схема и условное обозначение NMOS с собственным каналом

Часто терминал базы подключают напрямую к истоку.

Реализация логических операций на МОП-транзисторах

Независимо от типа транзистора, он может быть “настроен” таким образом, чтобы либо переходить в “открытое” состояние при подаче высокого напряжения (соответствующего логической единице) на затвор, либо низкого (соответствующего логическому нулю), и в “закрытое” в противном случае. При проектировании логических схем, имеет значение только этот фактор.

В этом контексте, транзисторы, переходящие в “открытое” состояние при подаче логической единицы на затвор, называются прямыми, а в “закрытое” – инверсными. При проектировании логики, часто используются следующие обозначения:

Прямой МОП-транзистор

Инверсный МОП-транзистор

Как правило, прямые транзисторы реализуются на NMOS, а инверсные – на PMOS.

На основе этих двух типов строятся микросхемы типа CMOS (КМОП – комплементарная структура металл-оксид-полупроводник, она же COS-MOS), состоящие из симметрично расположенных p- и n-канальных полевых транзисторов. Использование симметричных схем позволяет значительно уменьшить ток активации схемы, и снизить энергопотребление.

Штрих Шеффера может быть реализован, например, так:

VccF = A | BAB

Штрих Шеффера на прямых транзисторах

VccAVccBF = A | B

CMOS-схема штриха Шеффера Физическое устройство CMOS-схемы

Физическое устройство CMOS-схемы

Классификация и типы синхронизации триггеров

Триггеры делятся на два больших класса:

Принципиальное различие между ними в том, что у первой категории устройств уровень выходного сигнала меняется одновременно с изменением сигнала на входе (входах). У синхронных триггеров изменение состояния происходит только при наличии сихронизирующего (тактового, стробирующего) сигнала на предусмотренном для этого входе. Для этого предусмотрен специальный вывод, обозначаемый буквой С (clock). По виду стробирования синхронные элементы делятся на два класса:

У первого типа уровень выхода меняется в зависимости от конфигурации входных сигналов в момент появления фронта (переднего края) или спада тактового импульса (зависит от конкретного вида триггера). Между появлением синхронизирующих фронтов (спадов) на входы можно подавать любые сигналы, состояние триггера не изменится. У второго варианта признаком тактирования является не изменение уровня, а наличие единицы или нуля на входе Clock. Также существуют сложные триггерные устройства, классифицируемые по:

- числу устойчивых состояний (3 и более, в отличие от 2 у основных элементов);

- числу уровней (также более 3);

- другим характеристикам.

Сложные элементы имеет ограниченное применение в специфических устройствах.

Краткие теоретические сведения

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений).

Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

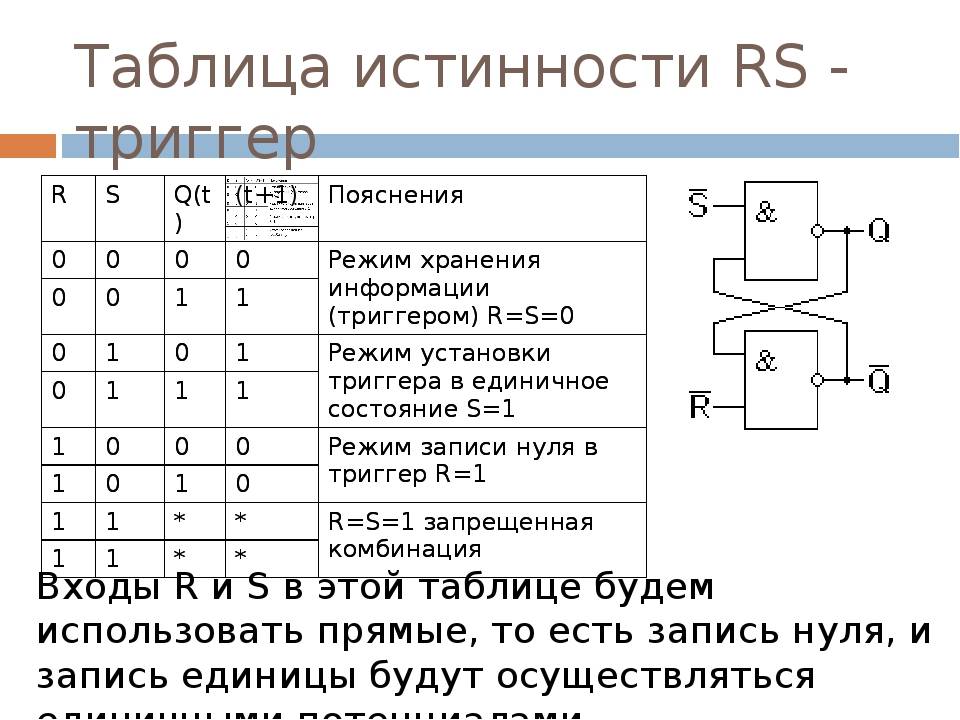

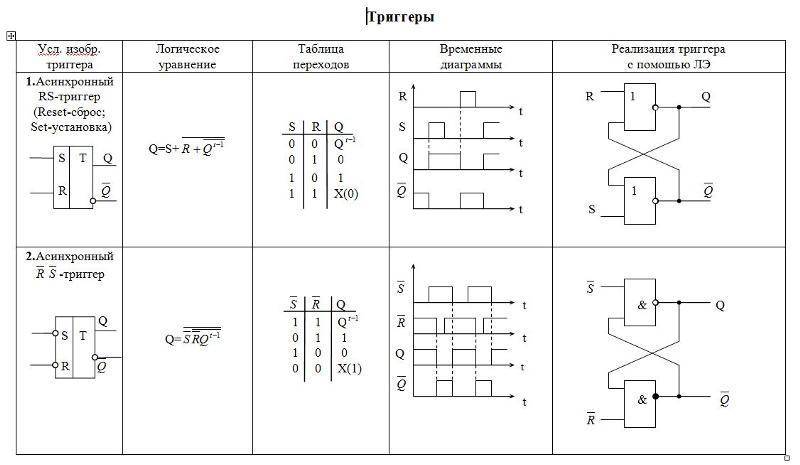

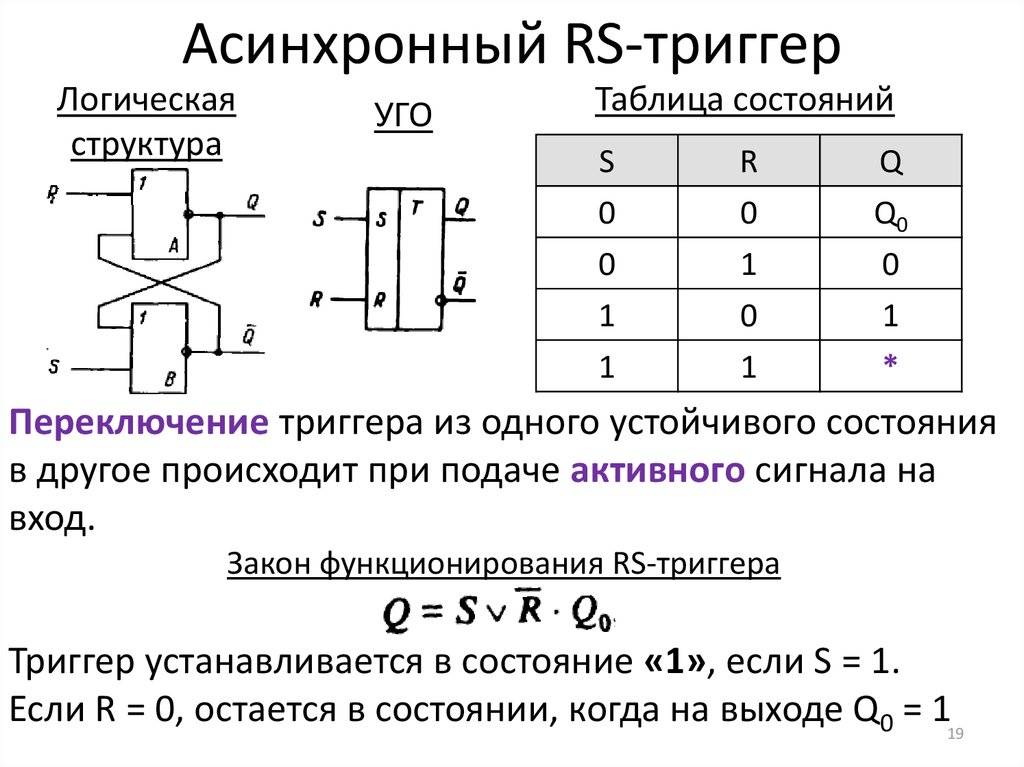

RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер. RS-триггер имеет два логических входа:

- R – установка 0 (от слова reset);

- S – установка 1 (от слова set).

RS-триггер имеет два выхода:

- Q – прямой;

- Q- обратный (инверсный).

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью.

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль – со входа R, другой – с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента.

Будет интересно Что такое электрическое поле: объяснение простыми словам

Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в “0”. Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния. Для описания работы триггера используют таблицу состояний (переходов). Обозначим:

- Q(t) – состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

- Q(t+1) – состояние триггера после изменения на входах R и S.

Таблица переходов RS триггера в базисе ИЛИ-НЕ

| R | S | Q(t) | Q(t+1) | Пояснения |

| Режим хранения информации R=S=0 | ||||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=1 | ||

| 1 | 1 | 1 | ||

| 1 | Режим установки нуля R=1 | |||

| 1 | 1 | |||

| 1 | 1 | * | R=S=1 запрещённая комбинация | |

| 1 | 1 | 1 | * |

RS-триггер можно построить и на элементах “И-НЕ” (рисунок 2.2).

Входы R и S инверсные (активный уровень “0”). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов “0”. Комбинация R=S=0 является запрещённой.

Таблица переходов RS триггера в базисе “2И-НЕ”

| R | S | Q(t) | Q(t+1) | Пояснения |

| * | R=S=0 запрещённая комбинация | |||

| 1 | * | |||

| 1 | Режим установки нуля R=0 | |||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=0 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | Режим хранения информации R=S=1 | ||

| 1 | 1 | 1 | 1 |

Синхронный RS-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс (в цифровых схемах этот процесс называется “опасные гонки”), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала).

Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера приведена.

Таблица переходов синхронного RS-триггера

| R | S | C | Q(t) | Q(t+1) | Пояснения |

| 1 | Режим хранения информации R = S = 0 | ||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы S =1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим установки нуля R=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | * | R = S = 1 запрещённая комбинация | |

| 1 | 1 | 1 | 1 | * |

В таблице 2.3. под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние.

Входы и виды триггеров

В зависимости от структуры и выполняемых им функций можно определить число входов триггера.

По параметру записи информации триггеры можно разделить на:

- Синхронные – запись информации производится только при дополнительном, синхронизирующем сигнале, который, по сути, запускает триггер.

- Асинхронные – запись информации зависит от информационных сигналов, подающихся на вход триггера, и происходит она непрерывно.

В цифровой схемотехнике обычно можно найти следующие обозначения входов триггера:

- S – раздельный вход, устанавливающий триггер на единицу (на Q единица)

- Q – прямой выход

- R – раздельный выход, устанавливающий триггер на ноль (на Q ноль)

- С – вход синхронизации

- D – вход информационный (на него подаётся информация, которая будет занесена на триггер)

- T – счётный вход

Что касается функций, то в этом плане триггеры можно разделить на:

- RS-триггеры;

- JK-триггеры;

- D-триггеры;

- Т-триггеры.

RS- триггер

Это самый простой тип триггеров. На его основе создаются и другие типы. Возможные логические элементы в его построении – это 2И-НЕ (инверсионный вход) и 2ИЛИ-НЕ (прямые входы).

Из-за низкой помехоустойчивости такие триггеры почти не используются самостоятельно. Их можно применить, например, для устранения влияния дребезжащих контактов, которое возникает при коммутации механических переключателей. Тогда требуется тумблер с тремя выходами, один из которых подключается по очереди к остальным двум. Чтобы создать RS-триггер используется D-триггер с замкнутыми на состоянии «ноль» входы С и D.

Первый отрицательный сигнал на входе –R переводит в состояние «0». Первый отрицательный сигнал на входе –S переводит в состояние «1». Другие сигналы, возникшие из-за дребезга контактов, не могут оказать влияние на триггер. При таком подключении переключателя верхнее положение будет равно «1» на выходе, нижнее – «0».

RS-триггер сам по себе асинхронный, однако, иногда возникают случаи, когда нужно сохранить информацию. Тогда на помощь приходит синхронизируемый RS-триггер, который в этом случае должен состоять из обычного RS-триггера и схемы управления.

При этой схеме, импульсы, поступающие на Х1 и Х2 не имеют никакого значения, пока на входе С сохраняет значение «0». В этот момент RS-триггер находится в режиме хранения информации. Как только значение C становится равно «1» триггер запускается, начинается запись.

D-триггер

Это триггеры задержки. Используются они для создания регистров сдвига и хранения. Это одна из важнейших частей всех микропроцессоров.

У такого триггера два выхода – информационный и синхронизирующий. Триггер стабилен, когда состояние С находится на «ноль». При этом сигнал на выходе не будет зависеть от сигналов, которые поступают на информационный вход. Когда значение С изменяется на «1» на прямом выходе, тогда информация будет такой же, как и на триггере D.

JK-триггер

По своему принципу действия он очень похож на RS- триггеры. Но в отличие от него, у JK-триггеров нет проблем с неопределённостью, когда на вход одновременно поступают две «единицы». При возникновении подобной ситуации JK-триггер становится счётным триггером. Тогда при поступлении на вход сигналов со значением «1» триггер меняет своё состояние на противоположное.

Эти устройства очень универсальны. С одной стороны, они прекрасно находят своё применение в цифровых устройствах – счётчиках, регистрах, делителях частоты и т.д. С другой стороны при соединении определённых выводов можно получить вообще любой нужный вид триггера.

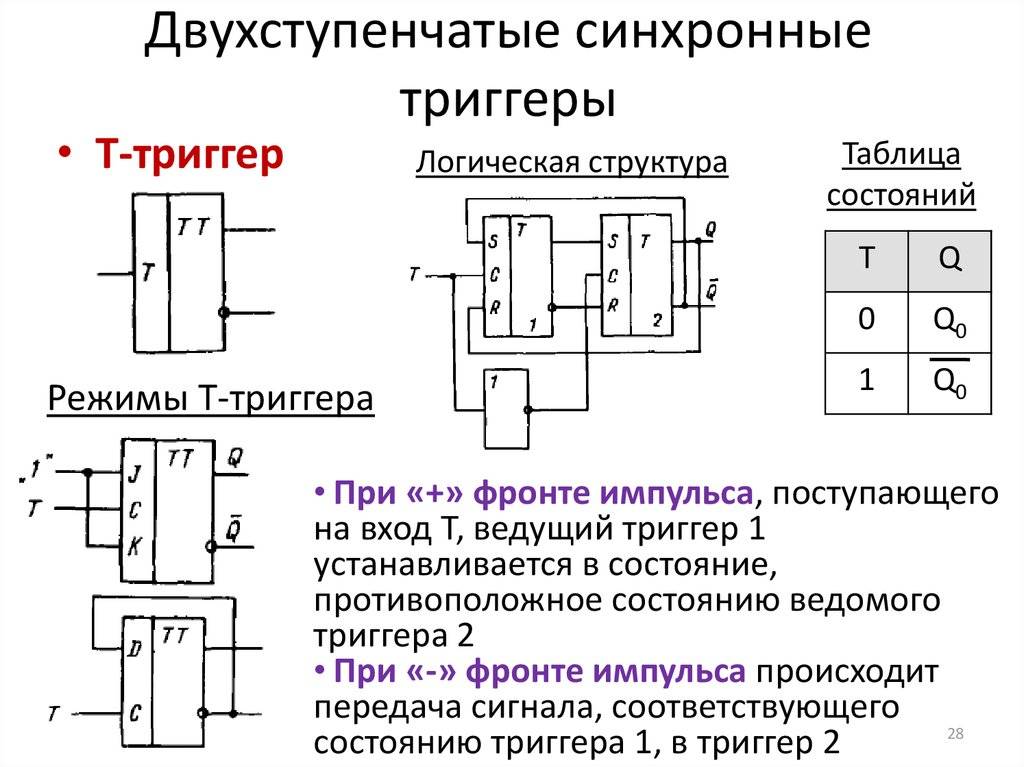

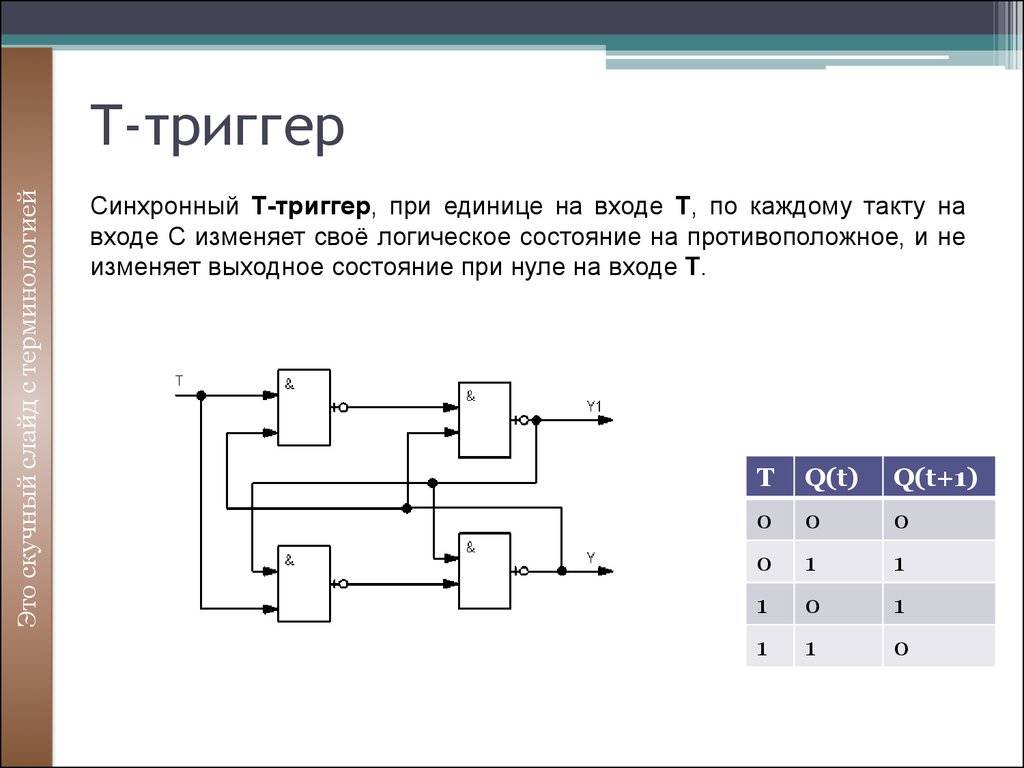

Т-триггер

У этих триггеров есть и другое название – счётные. На их основе создаёт двоичные счётчики и делители частот. У этих триггеров вход только один. На изображениях – асинхронный (1) и синхронный (2) Т-триггеры.

Импульс поступает на этот вход, состояние его меняется не противоположное. После поступления следующего импульса состояние становится исходным.

Триггер переключается в тот момент, когда на его вход поступается синхроимпульс. Тогда частота импульсов на выходе оказывается в 2 раза меньше начальной. Таким образом, один счётный триггер уменьшает частоту импульса двукратно. А два триггера, что были подключены последовательно, логично уменьшат частоту уже в 4 раза.

Почему эти триггеры называют ещё и делителями частот хорошо заметно по временным схемам: